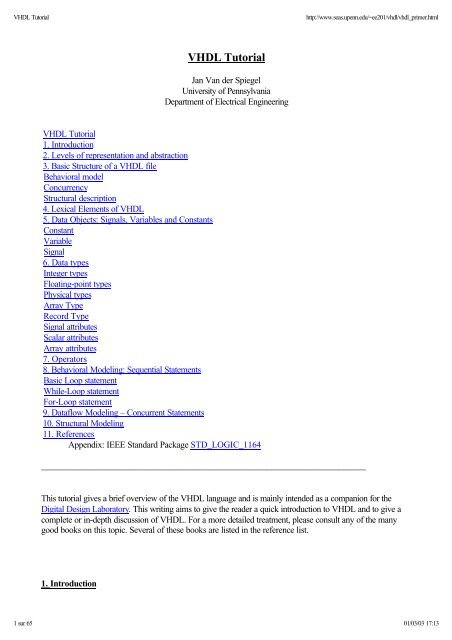

Vhdl Language

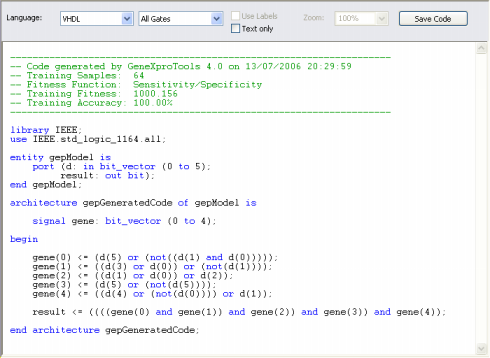

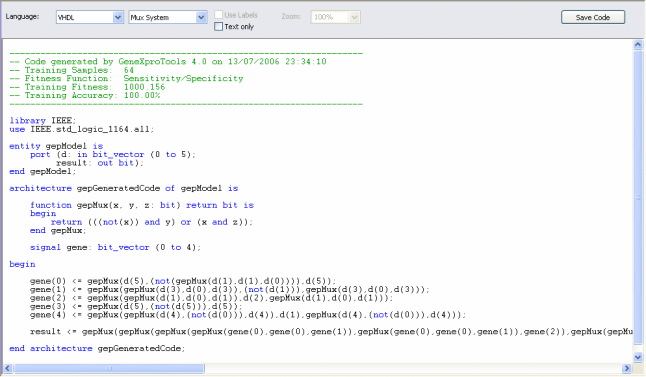

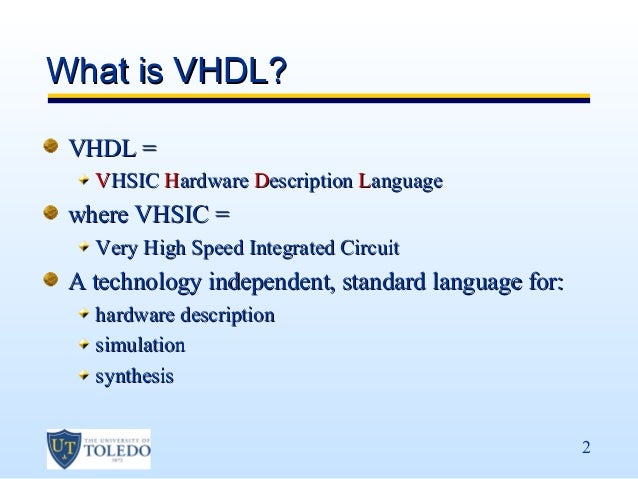

Vhdl very high speed integrated circuit hardware description language is standardized by ieee1164.

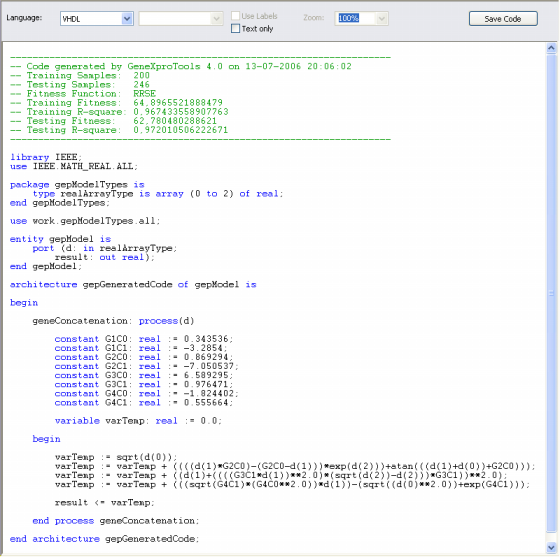

Vhdl language. The vhdl golden reference guide is a compact quick reference guide to the vhdl language its syntax semantics synthesis and application to hardware design. You might first benefit from an introduction to fpgas and asics if you are unfamiliar with these fascinating pieces of circuitry. Such a model is processed by a synthesis program only if it is part of the logic design. Unlike that document the golden reference guide does not offer a complete formal description of vhdl.

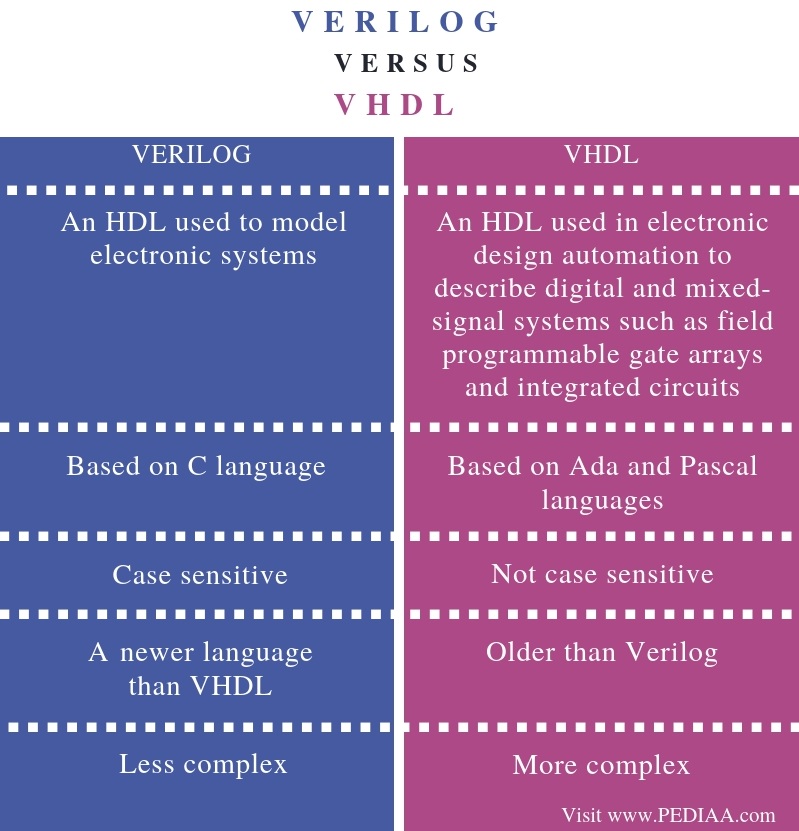

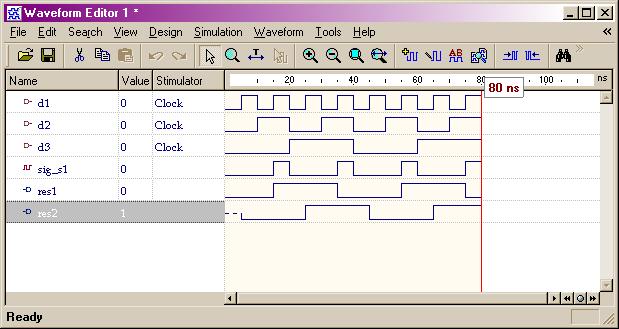

A simulation program is used to test the logic design using simulation models to represent the logic circuits that interface to the design. Vhdl stands for very high speed integrated circuit hardware description language. Vhdl is a hardware description language hdl that contains the features of conventional programming languages such as pascal or c logic description languages such as abel hdl and netlist languages. Phew that s a mouthful.

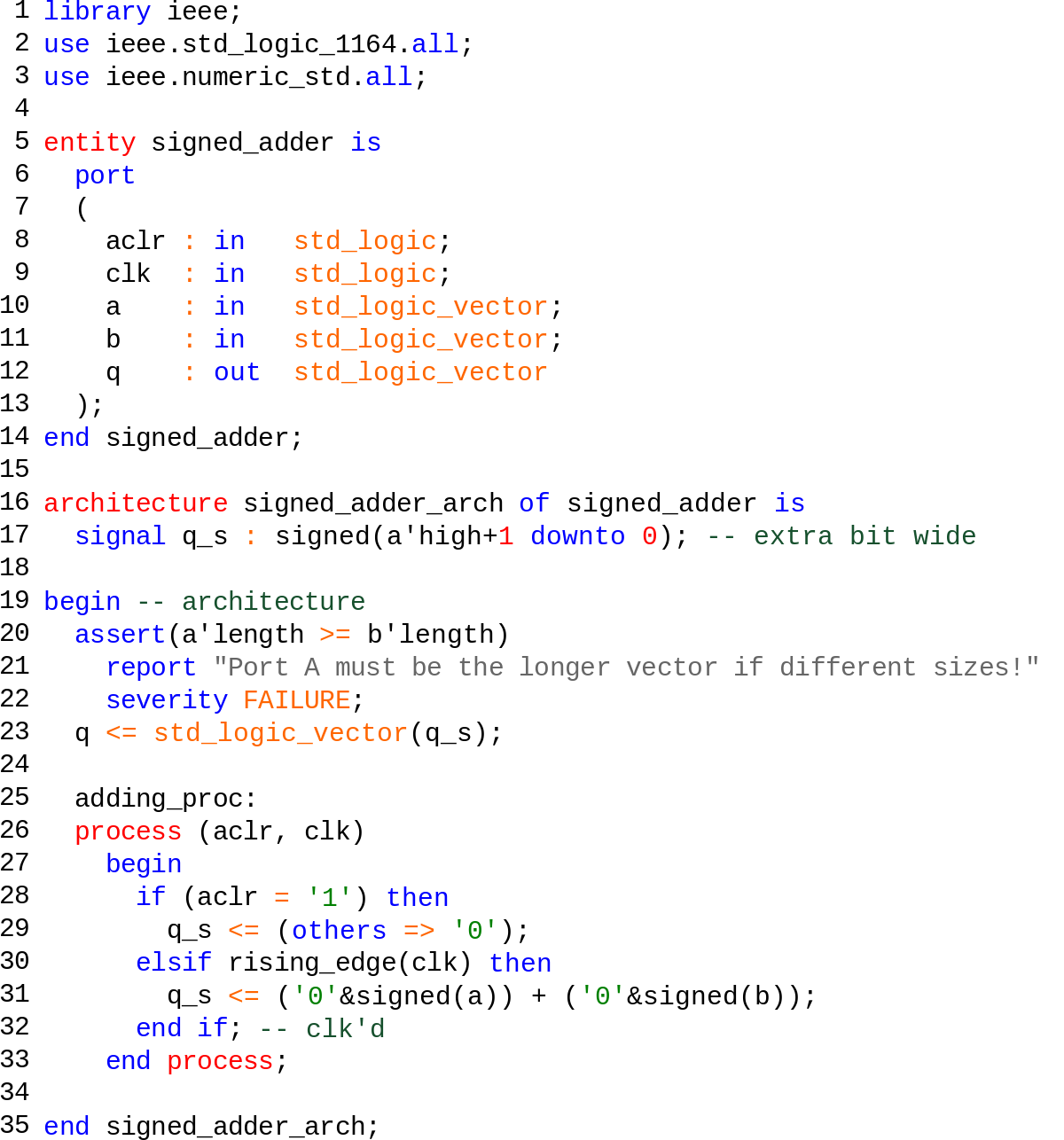

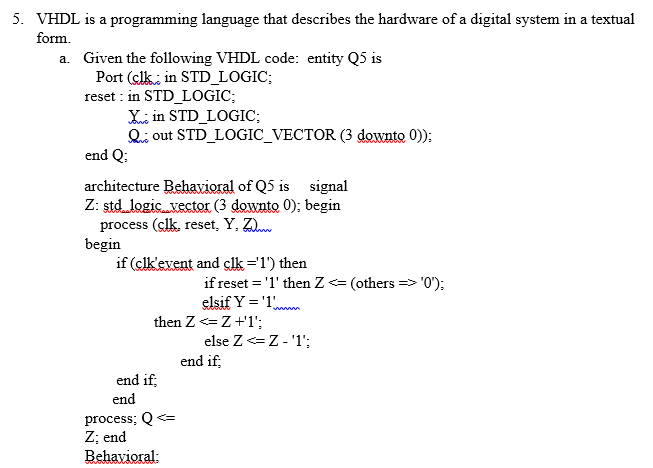

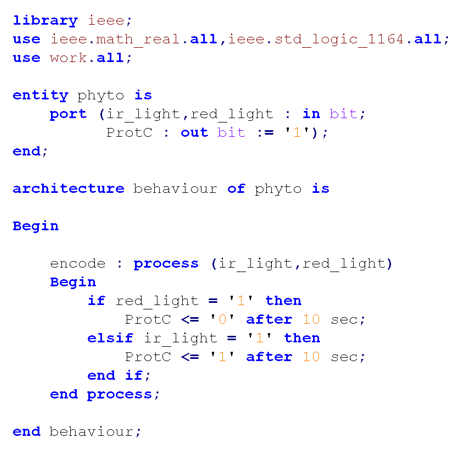

Systemc is a language that consist a set of c classes and macros. Sincevhdl is a strongly typed language one cannot assign a value of one data type toa signal of a different data type. Vhdl is a programming language that has been designed and optimized for describing the behavior of digital systems. The vhdl golden reference guide is not intended as a replacement for the ieee standard vhdl language reference manual.

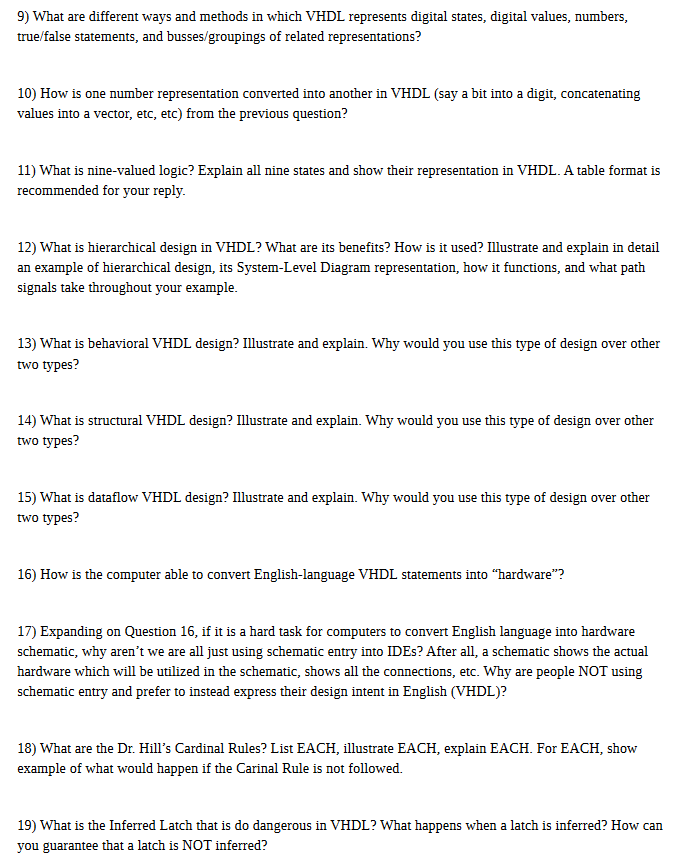

Vhdl and verilog are the two languages digital designers use to describe their circuits and they are different by design than your traditional software. Vhdl is a formal notation intended for use in all phases of the creation of electronic systems. It is a programming language used to model a digital system by dataflow behavioral and structural style of modeling. In general it is preferred to the same datatypes for the signals in a design such as std logic instead of a mix ofstd logic and bit types.

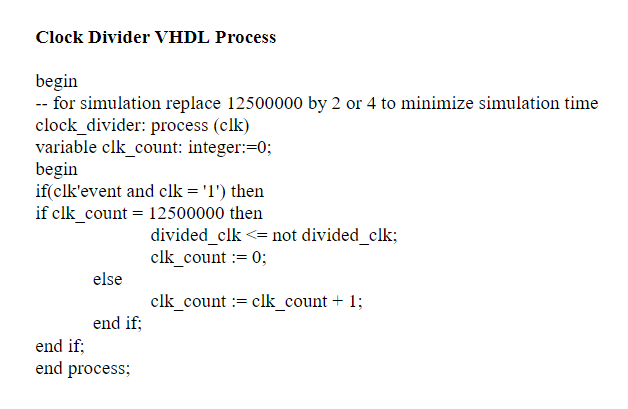

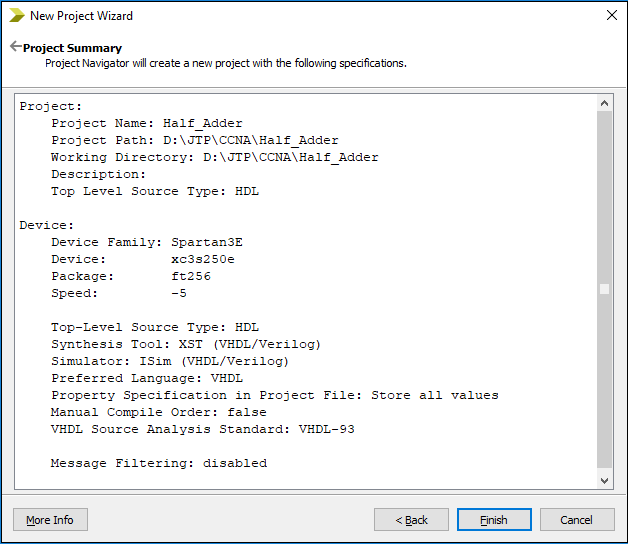

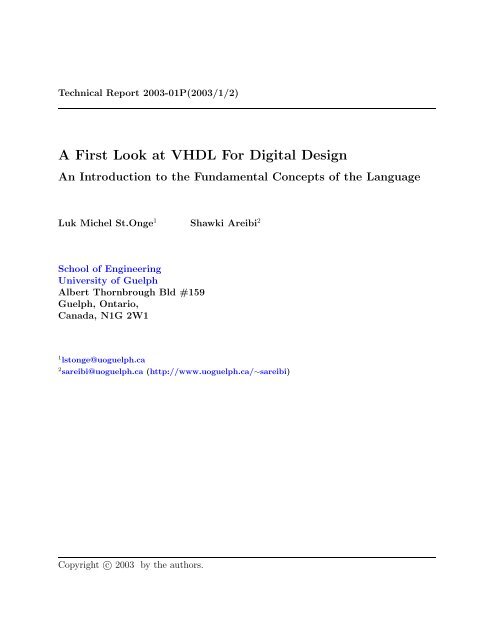

To provide context it shows where vhdl is used in the fpga design flow. Sometimes one cannot avoid using different types. It describes the use of vhdl as a design entry method for logic design in fpgas and asics. Vhdl is generally used to write text models that describe a logic circuit.

Vhsic hardware description language vhdl is defined. Therefore vhdl expanded is very high speed integrated circuit hardware description language. Vhdl has many features appropriate for describing the behavior of electronic components ranging from simple logic gates to complete microprocessors and custom chips. This language was first introduced in 1981 for the department of defense dod under the vhsic program.

Because it is both machine read able and human readable it supports the development verification synthesis and testing of hard. Vhdl is one of the two languages used by education and business to design fpgas and asics.